6层PCB推荐叠层方案为S-G-S-P-G-S结构(信号-地-信号-电源-地-信号),该方案兼顾信号完整性、电源完整性和EMC性能,是高速高密度设计的首选方案。

核心推荐方案

S-G-S-P-G-S结构(TOP信号/GND/S3信号/PWR/GND/BOTTOM信号)。

优势:

3个信号层与3个参考平面交替布局,高速信号(如PCIe、DDR4)可优先布置在S3层,上下均有地平面屏蔽。

电源层与地平面相邻(间距建议8-10mil),退耦电容效果提升40%。

对称叠层设计,降低板翘风险(翘曲度<0.5%)。

适用场景:AI服务器、5G通信、车载控制器等高频高密度场景。

备选方案

S-G-P-S-G-S结构(TOP信号/GND/PWR/S4信号/GND/BOTTOM信号)。

特点:

电源层居中,适合多电压系统(如CPU核心+外围电源)。

S4信号层参考电源平面,需注意阻抗匹配(差分线宽/间距建议4.5/5.5mil)。

缺点:电源与地平面分离,需增加去耦电容。

S-S-G-P-G-S结构(TOP信号/S2信号/GND/PWR/GND/BOTTOM信号)。

适用性:低频高电流场景(如电机驱动板),S2层可布置大电流走线(线宽≥1mm)。

风险:相邻信号层(S2与TOP)易产生串扰,需预留≥3倍线宽间距。

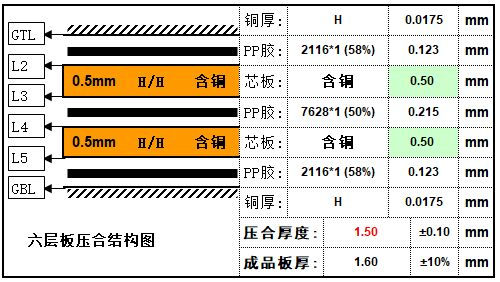

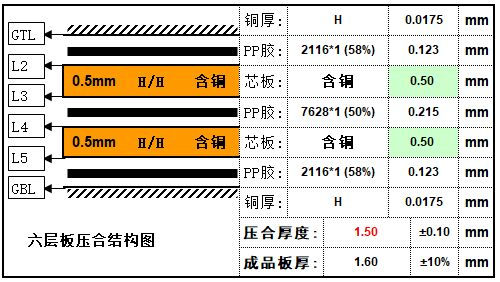

关键设计参数

介质厚度:

电源层与地平面间采用薄芯板(8mil FR-4),提升平面电容(容值≈0.5nF/cm²)。 信号层与参考平面间距建议5-8mil,阻抗波动≤±5%。

高速信号处理:

时钟线优先布置在中间信号层(S3),与电源层保持3倍线距以降低抖动。

避免平行走线,采用正交布局减少串扰。